重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目

更多“设计一个时序电路,它有两个输入X1和X0、一个输出Z0只有当X1;输入三个(或三个以上)1后,X0再输入一个1时,输出Z为1,而在同一时刻两个输入不同时为1,一旦Z=1,电路就回到原始状态。这里,X1…”相关的问题

更多“设计一个时序电路,它有两个输入X1和X0、一个输出Z0只有当X1;输入三个(或三个以上)1后,X0再输入一个1时,输出Z为1,而在同一时刻两个输入不同时为1,一旦Z=1,电路就回到原始状态。这里,X1…”相关的问题

第1题

设计一个时序电路,只有在连续两个或两个以上时钟作用期间,两个输入信号X1和X0一致时,输出信号才是1,其余情况输出为0。

第3题

设计一个串行数据检测器,该检测器有一个输入端X,它的功能是对输入信号进行检测。当连续输入三个1(以及三个以上1)时,该电路输出Y=1,否则该电路输出Y=0。

第4题

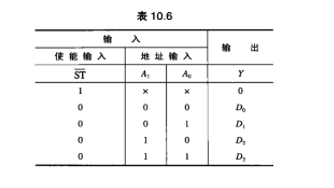

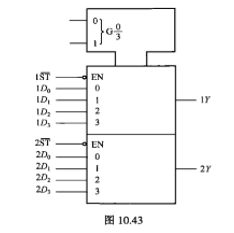

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y1、Y0的逻辑电路.电路输入为余3BCD码,输出为用2位二进制数表示的输入码中“1”的个数,例如,当输入X3X2X1X0=1010时,输出Y1Y0=10.当非余3码(伪码)输入时,要求输出Y1Y0=00.要求写出设计过程,画出电路图(规定X3、X2分别和数据选揮器地址码的高、低位相连接,74153的逻辑符号和功能表分别如图10.43和表10.6所示).

第6题

同步时序电路有一个输入端和一个输出端,输入为二进制序列X0X1X2…当输入序列中1的数目为奇数时输出为1,作出这个时序奇偶校验电路的状态图和状态表。

第7题

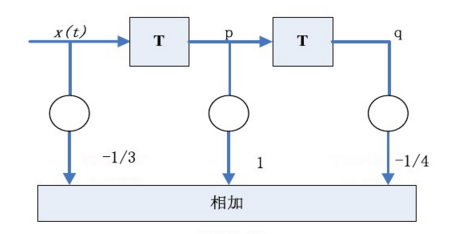

有一三抽头时域均衡器。各抽头增益分别为-1/3,1,1/4。若输入信号X(t)的抽样值为X-2=1/8,X-1=1/3,X0=1,X1=-1/4,X2=1/16,求均衡器输入及输出波形的峰值失真。

第9题

一个线性时不变系统有两个初始条件,x1(0)和x2(0),若 (1)x1(0)=1,x2(0)=0时,其零输入响应为yzi1(t)=(e-t+e-2t)ε(t); (2)x1(0)=0,x2(0)=1时,其零输入响应为yzi2(t)=一(e-t一e -2t)ε(t);已知激励为f(t)、x1(0)=1、x2(0)= ﹣l时,其全响应为(2+e-t)ε(t),试求激励为2f(t)、x1(0)=﹣l、x2(0)= ﹣2时的全响应y(t)。

第10题

图12.16所示是一个三人表决电路,只有两个或三个输入为1(表示赞成)时,输出才是1。试分析该电路能否实现这一功能。

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!