重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目

A.11.5,115

B.12.5,125

C.13.5,135

D.14.5,145

更多“两个加数的和是137.5,其中一个加数的小数点向左移动一位就等于另一个加数,求这两个加数分别是多少()”相关的问题

更多“两个加数的和是137.5,其中一个加数的小数点向左移动一位就等于另一个加数,求这两个加数分别是多少()”相关的问题

第1题

A.63

B.56

C.53

D.48

第2题

A.63

B.56

C.53

D.48

第3题

A.63

B.56

C.53

D.48

第4题

A.1

B.2

C.3

D.4

第7题

A.交换加数位置,再加一遍,看与和是否相同

B.用计算出的各减去其中一个加数,看是否等于另一个加数

C.用减数加差,看是否等于被减数

D.用和加加数,看是否等于另一个加数

第8题

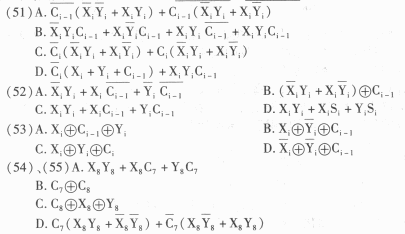

●全加器是由两个加数Xi和Yi以及低位来的进位C i-1作为输入,产生本位和Si以及向高位的进位Ci的逻辑电路。 (51) 和 (52) 分别是Si和Ci的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si= (53) 。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i=1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,C0=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为 (54) 和 (55) 。

第9题

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生本位和S,以及向高位的进位Ci的逻辑电路。(51)和(52)分别是Si和Ci的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(53)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i=1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,C0=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(54)和(55)。

A..jpg)

B..jpg)

C..jpg)

D..jpg)

第11题

A.addbit (r1, r2, ci, result, c1)

B.addbit (r1[0], r2[0], ci, result[0], c1)

C.addbit U0 (ci, r1[0], r2[0], result[0], c1)

D.addbit U0 (ci, r1[0], r2[0], cl, result[0])

E.addbit U0(r1[0], r2[0], ci, result[0], cl)

F.addbit, U0 (r1[0], r2[0], cl, result[0], ci)

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!