重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目

更多“试用数值比较器74HC85和必要的逻辑门设计一个余3码有效性测试电路,当输入为余3码时,输出为1,否则为0。”相关的问题

更多“试用数值比较器74HC85和必要的逻辑门设计一个余3码有效性测试电路,当输入为余3码时,输出为1,否则为0。”相关的问题

第2题

设计一个代码检测器,电路串行输入余3码,当输入出现非法数字时电路输出为0,否则为1,试作出Mearly状态图。

第3题

第4题

| 表3.2.1 | |

| 十进制数 | 余3码 |

| 0 | 0011 |

| 1 | 0100 |

| 2 | 0101 |

| 3 | 0110 |

| 4 | 0111 |

| 5 | 1000 |

| 6 | 1001 |

| 7 | 1010 |

| 8 | 1011 |

| 9 | 1100 |

第6题

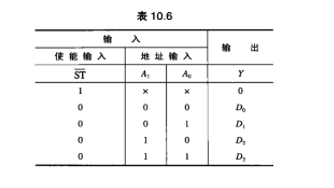

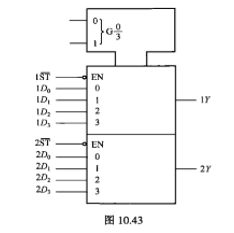

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y1、Y0的逻辑电路.电路输入为余3BCD码,输出为用2位二进制数表示的输入码中“1”的个数,例如,当输入X3X2X1X0=1010时,输出Y1Y0=10.当非余3码(伪码)输入时,要求输出Y1Y0=00.要求写出设计过程,画出电路图(规定X3、X2分别和数据选揮器地址码的高、低位相连接,74153的逻辑符号和功能表分别如图10.43和表10.6所示).

第7题

用MSI译码器和逻辑门,设计下列码组变换电路:

(1)8421码转换成余3码;

(2)8421码转换成2421码;

(3)8421码转换成格雷码。

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!