重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目

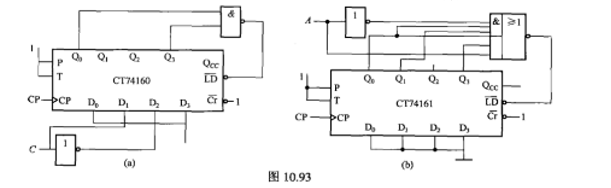

可控计数器,当控制信号C,A等于1和控制信号C,A等于0时,分别实现几进制计数器.

(2)用74161实现91进制计数器.

更多“(1)如图10.93(a)和10.93(b)所示的十进制加法计数器CT74160和4位二进制加法计数器CT74161构成的”相关的问题

更多“(1)如图10.93(a)和10.93(b)所示的十进制加法计数器CT74160和4位二进制加法计数器CT74161构成的”相关的问题

第1题

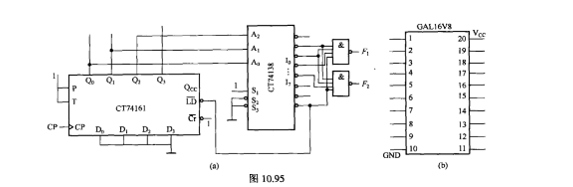

转换图.假设Q3Q2Q1Q0的初始状态均为0,说明CT74161构成几进制计数器.

(2)说明C174138电路实现的功能.

(3)写出图10.95(a)完成的电路功能符合ABEL语言(GAL16V8如图10.95(b)所示)或VHDL语言的用户原文件(可省略测试向量段).

第3题

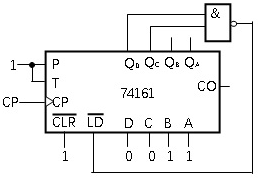

用一片如图A1-4所示的4位二进制加法计数器74161和必要的逻辑门电路设计一个可控计数器,要求当控制信号M=1时,实现七进制计数器;而当控制信号M=0时,实现十三进制计数器。画出所设计的可控计数器的逻辑电路。

第4题

A.余3码编码的十进制加法计数器

B.循环码编码的九进制加法计数器

C.余3码编码的三进制加法计数器

D.循环码编码的二进制加法计数器

第5题

位二进制加法计数器CT74161和集成单稳态触发器CT74LS121组成如图P6.10(a)所示的电路.

(1)分析CT74161组成电路,画出转换状态图.

(2)估算CT74LS121组成电路的输出脉宽Tw值.

(3)设CP为方波(周期Td≥1ms),在图P6.10(b)中画出图P6.10(a)中u1、u0两点的工作波形.

第6题

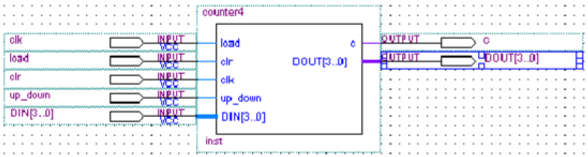

4位二进制加法计数器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计4位二进制加法计数器电路,建立4位二进制加法计数器的实验模式。通过电路仿真和硬件验证,进一步了解4位二进制加法计数器的功能和特性。

设计原理

4位二进制加法计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;CLRN是复位输入端,低电平有效;Q[3..0]是计数器的状态输出端;COUT是进位输出端。

第7题

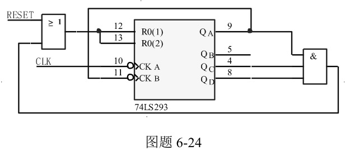

图题 6-24所示为异步4位二进制加法计数器74LS293组成的计数器电路,

试说明该计数电路是多少进制计数器,并说明复位信号RESET的有效电平,

第8题

试用集成4位二进制加法计数器74LS161构成十二进制计数器。

(1)用反馈复位法实现。

(2)用反馈置数法实现。

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!