重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目

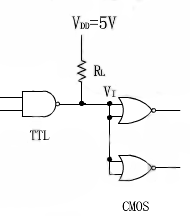

如图题2.10所示是用TTL电路驱动CMOS电路的实例,试计算上拉电阻RL的取值范围。TTL与非门输出为低电平VOL≤0.4V时,允许的最大灌电流为ILM= 8mA,输出为高电平VOH≥3.2V时,输出电流最大值为ION(max)=-0.4mA。CMOS或非门的输入电流可以忽略,电源电压VDD=5V。

更多“如图题2.10所示是用TTL电路驱动CMOS电路的实例,试计算上拉电阻RL的取值范围。TTL与非门输出为低电平VOL≤0.4V”相关的问题

更多“如图题2.10所示是用TTL电路驱动CMOS电路的实例,试计算上拉电阻RL的取值范围。TTL与非门输出为低电平VOL≤0.4V”相关的问题

第1题

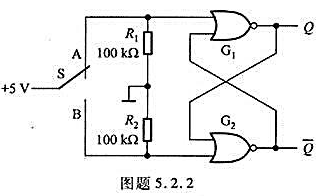

如图题2.16所示TTL与非门电路,如果用内阻为20kn/ΩV的万用表测量输入端B的电压,试问在下列情况下,测到的电压值为多少?

(1) 输入端A悬空;

(2) 输入端A接在Vcc上;

(3) 输入端A通过一个10kΩ的电阻接地;

(4) 输入端A通过一个10Ω的电阻接地;

(5) 输入端接高电平(3.2V);

(6) 输入端接低电平(0.2V)。

第2题

第3题

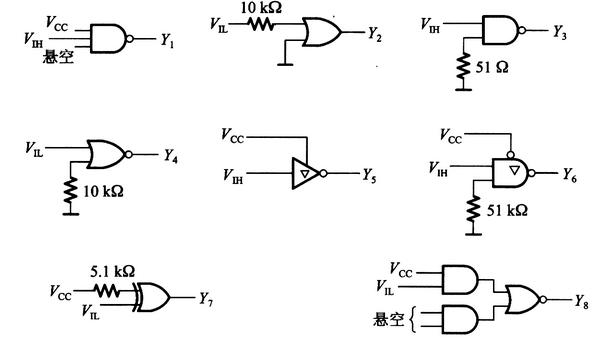

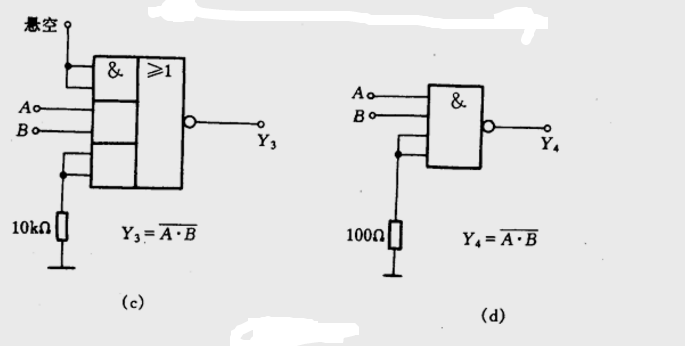

如图题2.6所示的门电路均为TTL门电路,试指出各门电路的输出是什么状态(高电平、低电平或高阻态)。

第4题

如图由74系列TTL门组成的电路中,计算门CM能驱动多少同样的与非门。要求GM输出的高、低电平满足VOH≥3.2V,VOL≤0.4V。与非门的输入电流IIL≤-1.6mA,IIH≤40μA。VOL≤0.4V时输出电流的最大值,IOL(max)=16mA,VOH≥3.2V时输出电流的最大值为IOH(max)=-0.4mA。GM的输出电阻可忽略不计。

第5题

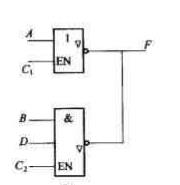

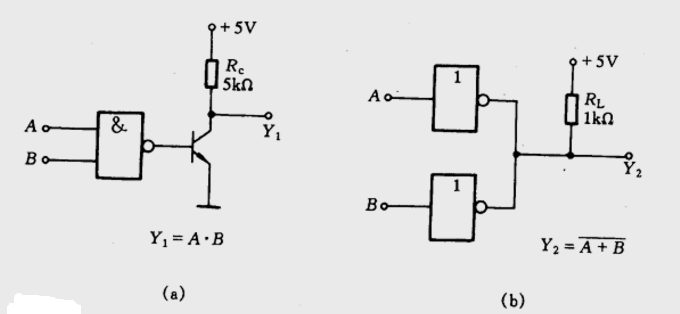

如图题2.12所示的4个电路中,要实现相应表达式规定的逻辑功能,电路连接有什么错误?请改正之。

(1) 电路中所示均为TTL电路。

(2) 电路中所示均为CMOS电路。

第6题

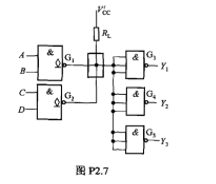

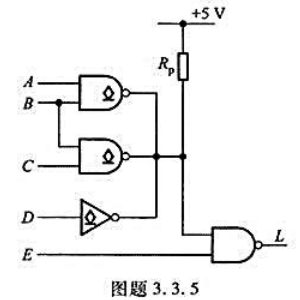

电路如图P2.7所示,两个OC门驱动三个TTL与非门,已知V'cc=5V,与非门的低电

平输入电流为IIL=1mA,高电平输入电流为IDH=40μA、OC门截止时的漏电流为IOH=200uA,导通时允许的最大负载电流为ILM=16mA要求OC门输出的高电平UOH≥3V,低电平UOL≤0.4V.试求电路中外接负载电阻RL的取值范围.

第7题

路,写出符合VHDL规范的用户源文件.

第8题

第10题

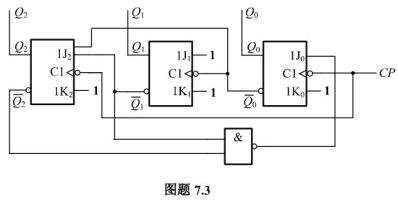

计数器电路如图题7.3所示。设各触发器的初始状态均为“0”,要求:

(1) 写出各触发器的驱动方程和次态方程;

(2)画出次态卡诺图;画出状态转换图并说明该计数器电路的逻辑功能;

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!