重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目

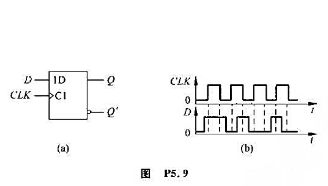

画出图P5.9(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CIK和输入端D的电压波形如图P5.9(b)所示。设触发器的初始状态为Q-0。

更多“画出图P5.9(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CIK和输入端D的电压波形如图”相关的问题

更多“画出图P5.9(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CIK和输入端D的电压波形如图”相关的问题

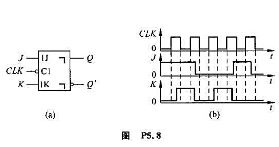

第1题

图P5.8(b)所示。设触发器的初始状态为Q=0。

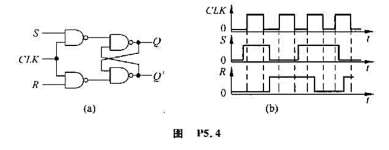

第2题

4(b)所示。设触发器的初始状态为Q=0。

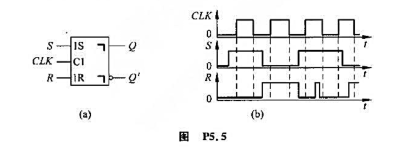

第3题

5.5(b)所示。设触发器的初始状态为Q=0。

第4题

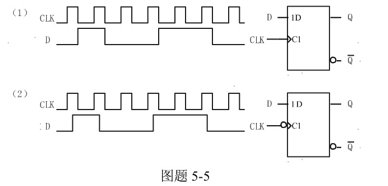

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

第5题

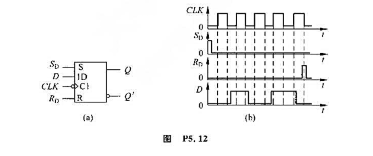

在图P5.12(a)下降触发D触发器中,已知时钟脉冲CLK、输入端D、异步置位输入端RD和异步复位输入端RD的电压波形如图P5.12(b)中所示,试画出输出端Q对应的电压波形。

第6题

画出图P5.15(a)中两个T触发器FF1和FF2的输出端Q1和Q2的电压波形。时钟脉冲CLK和输入端T的电压波形如图P5.15(b)所示。设触发器的初始状态均为Q=0。

第7题

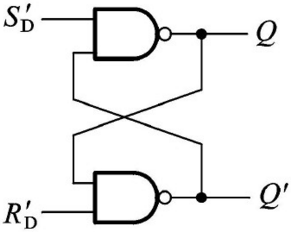

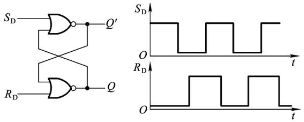

画出图5.1.1由与非门组成的SR锁存器输出端Q、Q'的电压波形,输入端S'D、R'D的电压波形如图5.1.1所示。

第8题

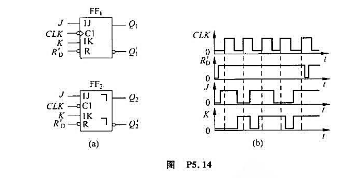

异步置零端R´D和输入端J、K的电压波形如图P5.14(b)所示。设触发器的初始状态均为Q=0。

第9题

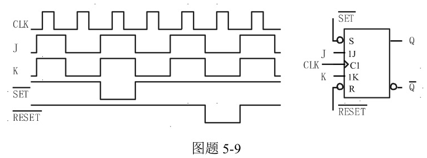

画出图题5-9所示的正边沿触发JK触发器输出Q端的波形,输入端J、K与CLK的波形如图所示。(设Q初始状态为0)

第10题

画出图5.2.1由或非门组成的SR锁存器输出端Q、Q'的电压波形,输入端SD、RD的电压波形如图5.2.1所示。

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!